# UNIVERSITY OF BOLTON

# SCHOOL OF ENGINEERING

# MSC SYSTEMS ENGINEERING AND ENGINEERING MANAGEMENT

# SEMESTER 2 EXAMINATION 2023/2024

# **MICROPROCESSOR BASED SYSTEMS**

**MODULE NO: EEM7016**

Date: Thursday 16<sup>th</sup> May 2024 Time: 10:00 – 12:00pm

**INSTRUCTIONS TO CANDIDATES:** There are SIX questions.

Answer ANY FOUR questions.

All questions carry equal

marks.

Marks for parts of questions are

shown in brackets.

Electronic calculators may be used provided that data and program storage memory is cleared prior to the

examination.

<u>CANDIDATES REQUIRE:</u> PIC18F452 data sheet (attached).

# Question 1.

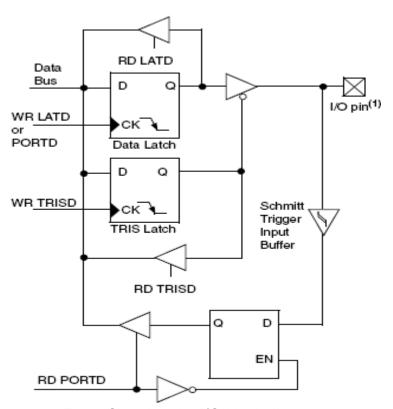

a) Describe the registers' operation of the Input/Output (I/O) port of the PIC18F452 shown in Fig.1.

(6 marks)

b) Use the I/O block diagram shown in Fig.1 to configure the port noted as an Input/Output (I/O) pin for input.

(7 marks)

c) Use the Input/Output (I/O) block diagram shown in Fig.1 to configure the port noted as I/O pin for output High (HI).

(7 marks)

Fig.1: Showing the I/O block diagram.

d) Explain how to use Read/Modify/Write Bit-wise operators to set Bit-2 without changing other bits by assuming the initial value of LATD register is 01101001.

(5 marks)

**Total 25 marks**

## Question 2.

a) Describe the differences between the following codes: Machine Code, Assembly Code, and 'C' Code.

(6 marks)

- b) What is the difference between a 'while' loop and a 'do while' loop in 'C'? Explain this difference in terms of the execution methodology and code syntax of each one.

(4 marks)

- c) Write a function in C language named min () that returns the minimum value of three arguments that are passed to the function when it is called. Assume that all three arguments will be of the float data type.

(7 marks)

d) Write a program in C language to add two matrices A[4][3] and B[4][3].

(8 marks)

**Total 25 marks**

#### Question 3.

#### Part A - Select the correct choice below - maximum of 12 marks

1) A flowchart is a method to describe the software design where the rectangular symbol refers to

(2 marks)

- i. an instruction or a command.

- ii. a decision statements.

- iii. a jump from one point in the sequence to another.

- iv. a point where there is input to or output from the program.

- 2) The width of the data bus can be measured directly based on the (2 marks)

- largest number that the bus can carry.

- ii. smallest number that the bus can carry.

- iii. amount of memory a system can retrieve.

- iv. data and Instructions through the bus.

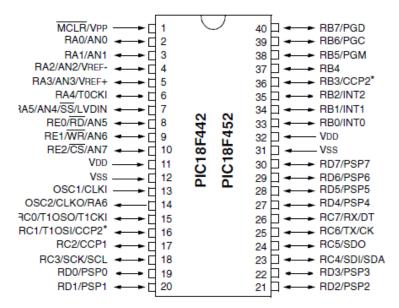

- 3) The PIC18F452 microcontroller device has

(2 marks)

- i. three bidirectional programming data ports.

- ii. four bidirectional programming data ports.

- iii. five bidirectional programming data ports.

- iv. six bidirectional programming data ports.

Q3 Part A continues over the page PLEASE TURN THE PAGE

## Q3 Part A continued

4) The steps order of the software part of the embedded system design is

(2 marks)

- i. Code the design, compile the code, algorithm design, program code to target, run the target and test.

- ii. Algorithm design, code the design, program code to target, compile the code, run the target and test.

- iii. Algorithm design, compile the code, code the design, program code to target, run the target and test.

- iv. Algorithm design, code the design, compile the code, program code to target, run the target and test.

- 5) One of the reserved keywords in C programming language is: (2 marks)

- i. try

- ii. throw

- iii. catch

- iv. case

- 6) The incorrect identifier name of a variable in C language is

(2 marks)

- i. B6

- ii. b6.13

- iii. OK

- iv. X ray

# Part B - Write the required code to configure the LCD function shown in Fig.2 to perform the following commands: - maximum 13 marks

|      | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Code |    |     |     |     |     |     |     |     |     |     |

Fig.2: Showing LCD configuration.

| 1. | Display on/off control | (5 marks) |

|----|------------------------|-----------|

| 2. | Clear display          | (2 marks) |

| 3. | Return home            | (2 marks) |

| 4. | Write data             | (2 marks) |

| 5. | Read data              | (2 marks) |

Total 25 marks PLEASE TURN THE PAGE

Page 5 of 12

School of Engineering

MSc Systems Engineering and Engineering Management

Semester 2 Examination 2023/2024

Microprocessor Based Systems

Module No. EEM7016

## Question 4.

- a) Draw a state machine diagram for a simple children's moving toy. The toy moves in response to sound and stops when it touches an object. The specifications are as follows:

- The toy is switched on using a button click to Start.

- After turning it on the toy is Idle.

- If a sound is detected (label it as: "On Sound"), the toy will **Start Motor Forward**.

- It then carries on Moving Forward until it either touches an object (label it as: "On Touch") which then causes it to Stop or if another sound is detected, the toy should Start Motor Backward.

- Again, the toy continues Moving Backward until it either touches an object (label it as: "On Touch") which causes it to Stop or if another sound is detected (label it as: "On Sound"), the toy will Start Motor Forwards again.

When the toy is stopped, it will then move to the **Idle** position and **Start Motor**Forward if a sound is detected. (12 marks)

b) Write a C code function under the name "StateMachineToy" using switch case statement for implementing the state machine diagram that you created in part-a.

(13 marks)

**Total 25 marks**

# Question 5.

a) Write a C program to draw star-pattern of the shape below: (13 marks)

Fig.3: Showing a star-pattern of diamond.

- b) What is the role of the data and address bus in a computer Central processing Unit (CPU)? (4 marks)

- c) Compare the difference between Von-Neumann and Harvard architectures in terms of:

1. Memory organisation (4 marks)

2. Advantages (2 marks)

3. Disadvantages (2 marks)

**Total 25 marks**

# Page 7 of 12

School of Engineering MSc Systems Engineering and Engineering Management Semester 2 Examination 2023/2024 Microprocessor Based Systems Module No. EEM7016

# Question 6.

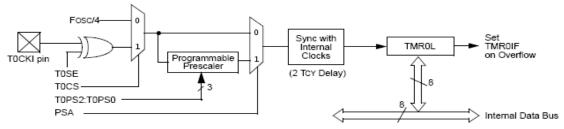

- a) The PIC18F452 has a 16-bit timer but the data bus is only 8-bits wide. Explain how a 16-bit timer read/write is carried out. (10 marks)

- b) The timer module of a PIC18F452 is configured as given below:

- Fosc = 4 MHz

- T0CON = 0xC2

- INTCON = 0xA0

At what rate will the interrupt occur if the TMR0 is pre-loaded with the value 131? (15 marks)

**Total 25 marks**

# **END OF QUESTIONS**

PLEASE TURN PAGE FOR PIC18F452 DATA SHEET

# **Data Sheet Information for the PIC18F452 Microcontroller**

TIMERO BLOCK DIAGRAM (8-BIT MODE)

Note: Upon Reset, Timer0 is enabled in 8-bit mode with clock input from T0CKI max. prescale.

Fig. 4: Timer0 Block Diagram.

### T0CON: TIMER0 CONTROL REGISTER

|   | R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---|--------|--------|-------|-------|-------|-------|-------|-------|

|   | TMR00N | T08BIT | T0CS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| • | bit 7  |        |       |       |       |       |       | bit 0 |

- bit 7 TMR00N: Timer0 On/Off Control bit

- 1 = Enables Timer0

- o = Stops Timer0

- bit 6 T08BIT: Timer0 8-bit/16-bit Control bit

- 1 = Timer0 is configured as an 8-bit timer/counter

- o = Timer0 is configured as a 16-bit timer/counter

- bit 5 T0CS: Timer0 Clock Source Select bit

- 1 = Transition on T0CKI pin

- o = Internal instruction cycle clock (CLKO)

- bit 4 T0SE: Timer0 Source Edge Select bit

- 1 = Increment on high-to-low transition on T0CKI pin

- o = Increment on low-to-high transition on T0CKI pin

- bit 3 PSA: Timer0 Prescaler Assignment bit

- 1 = TImer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler.

- o = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output.

- bit 2-0 TOPS2:TOPS0: Timer0 Prescaler Select bits

- 111 = 1:256 prescale value

- 110 = 1:128 prescale value

- 101 = 1:64 prescale value

- 100 = 1:32 prescale value

- 011 = 1:16 prescale value

- 010 = 1:8 prescale value

- 001 = 1:4 prescale value

- ooo = 1:2 prescale value

Fig. 5: Timer0 Control Register.

# Page 9 of 12

School of Engineering

MSc Systems Engineering and Engineering Management

Semester 2 Examination 2023/2024

Microprocessor Based Systems

Module No. EEM7016

# INTCON REGISTER

| R/W-0                                                                                                                   | R/W-0                                                                                              | R/W-0        | R/W-0       | R/W-0         | R/W-0        | R/W-0        | R/W-x     |  |  |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------|-------------|---------------|--------------|--------------|-----------|--|--|

| GIE/GIEH                                                                                                                | PEIE/GIEL                                                                                          | TMR0IE       | INT0IE      | RBIE          | TMR0IF       | INT0IF       | RBIF      |  |  |

| oit 7                                                                                                                   |                                                                                                    |              |             |               |              |              | bit 0     |  |  |

| bit 7                                                                                                                   | GIE/GIEH: GIO                                                                                      | bal Interrup | t Enable bi | t             |              |              |           |  |  |

|                                                                                                                         | When IPEN =                                                                                        | <u>o:</u>    |             |               |              |              |           |  |  |

|                                                                                                                         | 1 = Enables al                                                                                     |              | interrupts  |               |              |              |           |  |  |

|                                                                                                                         | o = Disables a<br>When IPEN =                                                                      |              |             |               |              |              |           |  |  |

| 1 = Enables all high priority interrupts o = Disables all interrupts                                                    |                                                                                                    |              |             |               |              |              |           |  |  |

|                                                                                                                         | o = Disables all interrupts                                                                        |              |             |               |              |              |           |  |  |

| bit 6 PEIE/GIEL: Peripheral Interrupt Enable bit When IPEN = 0:                                                         |                                                                                                    |              |             |               |              |              |           |  |  |

|                                                                                                                         | <u>When IPEN = </u><br>1 = Enables al                                                              | _            | poriphoral  | intorrunto    |              |              |           |  |  |

|                                                                                                                         | o = Disables a                                                                                     |              |             | interrupts    |              |              |           |  |  |

|                                                                                                                         | When IPEN =                                                                                        |              |             |               |              |              |           |  |  |

| when IPEN = 1:  1 = Enables all low priority peripheral interrupts  0 = Disables all low priority peripheral interrupts |                                                                                                    |              |             |               |              |              |           |  |  |

|                                                                                                                         |                                                                                                    |              |             |               |              |              |           |  |  |

|                                                                                                                         | bit 5 <b>TMR0IE:</b> TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 overflow interrupt |              |             |               |              |              |           |  |  |

|                                                                                                                         |                                                                                                    |              |             | •             |              |              |           |  |  |

| o = Disables the TMR0 overflow interrupt bit 4 INT0IE: INT0 External Interrupt Enable bit                               |                                                                                                    |              |             |               |              |              |           |  |  |

|                                                                                                                         | 1 = Enables th                                                                                     |              |             |               |              |              |           |  |  |

|                                                                                                                         | o = Disables th                                                                                    |              |             |               |              |              |           |  |  |

|                                                                                                                         | RBIE: RB Port                                                                                      |              |             |               |              |              |           |  |  |

|                                                                                                                         | 1 = Enables th<br>o = Disables tr                                                                  |              |             |               |              |              |           |  |  |

|                                                                                                                         | TMR0IF: TMR                                                                                        |              | •           | •             |              |              |           |  |  |

|                                                                                                                         | 1 = TMR0 regi                                                                                      |              |             | iust be clear | red in softw | are)         |           |  |  |

|                                                                                                                         | o = TMR0 regi                                                                                      |              |             |               |              |              |           |  |  |

|                                                                                                                         | INTOIF: INTO E                                                                                     |              |             |               |              |              |           |  |  |

|                                                                                                                         | 1 = The INT0 6<br>0 = The INT0 6                                                                   |              | •           | •             | e cleared in | soπware)     |           |  |  |

|                                                                                                                         | RBIF: RB Port                                                                                      |              | •           |               |              |              |           |  |  |

|                                                                                                                         | 1 = At least on                                                                                    | _            |             |               | ate (must b  | e cleared in | software) |  |  |

|                                                                                                                         | o = None of th                                                                                     |              |             |               |              |              |           |  |  |

Fig. 6: INTCON register.

Fig. 7: PIC18F452 Pinout

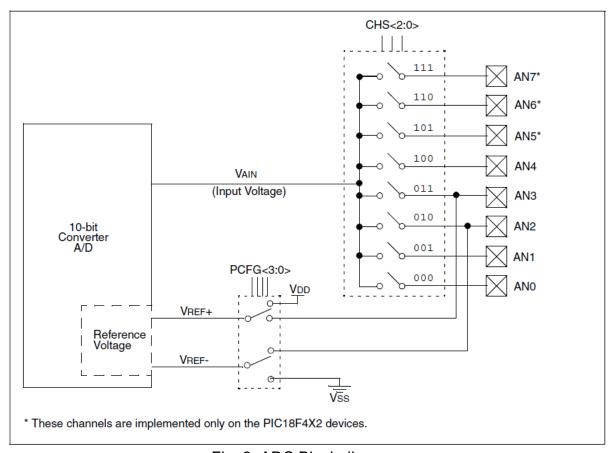

Fig. 8: ADC Block diagram.

# Page 11 of 12

School of Engineering

MSc Systems Engineering and Engineering Management

Semester 2 Examination 2023/2024

Microprocessor Based Systems

Module No. EEM7016

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | _   | ADON  |

| bit 7 |       |       |       |       | •       |     | bit 0 |

#### bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits (ADCON0 bits in bold)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

## bit 5-3 CHS2:CHS0: Analog Channel Select bits

000 = channel 0, (AN0)

001 = channel 1, (AN1)

010 = channel 2, (AN2)

011 = channel 3, (AN3)

100 = channel 4, (AN4)

101 = channel 5, (AN5)

110 = channel 6, (AN6)

111 = channel 7, (AN7)

Note: The PIC18F2X2 devices do not implement the full 8 A/D channels; the unimplemented selections are reserved. Do not select any unimplemented channel.

#### bit 2 GO/DONE: A/D Conversion Status bit

#### When ADON = 1:

- 1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically cleared by hardware when the A/D conversion is complete)

- 0 = A/D conversion not in progress

## bit 1 Unimplemented: Read as '0'

- bit 0 ADON: A/D On bit

- 1 = A/D converter module is powered up

- 0 = A/D converter module is shut-off and consumes no operating current

Fig. 9: ADCON0 Register.

# Page 12 of 12

School of Engineering MSc Systems Engineering and Engineering Management Semester 2 Examination 2023/2024 Microprocessor Based Systems Module No. EEM7016

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-------|-------|

| ADFM  | ADCS2 | _   | _   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |       |     |     |       |       |       | bit 0 |

- bit 7 ADFM: A/D Result Format Select bit

- 1 = Right justified. Six (6) Most Significant bits of ADRESH are read as '0'.

- 0 = Left justified. Six (6) Least Significant bits of ADRESL are read as '0'.

- bit 6 ADCS2: A/D Conversion Clock Select bit (ADCON1 bits in bold)

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 00                                    | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 00                                    | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits

| PCFG<br><3:0> | AN7 | AN6 | AN5 | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R |

|---------------|-----|-----|-----|-----|-------|-------|-----|-----|-------|-------|-----|

| 0000          | Α   | Α   | Α   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 8/0 |

| 0001          | Α   | Α   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 7/1 |

| 0010          | D   | D   | D   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 5/0 |

| 0011          | D   | D   | D   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 4/1 |

| 0100          | D   | D   | D   | D   | Α     | D     | Α   | Α   | VDD   | Vss   | 3/0 |

| 0101          | D   | D   | D   | D   | VREF+ | D     | Α   | Α   | AN3   | Vss   | 2/1 |

| 011x          | D   | D   | D   | D   | D     | D     | D   | D   | _     | _     | 0/0 |

| 1000          | Α   | Α   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 6/2 |

| 1001          | D   | D   | Α   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 6/0 |

| 1010          | D   | D   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 5/1 |

| 1011          | D   | D   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 4/2 |

| 1100          | D   | D   | D   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 3/2 |

| 1101          | D   | D   | D   | D   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 2/2 |

| 1110          | D   | D   | D   | D   | D     | D     | D   | Α   | VDD   | Vss   | 1/0 |

| 1111          | D   | D   | D   | D   | VREF+ | VREF- | D   | Α   | AN3   | AN2   | 1/2 |

A = Analog input D = Digital I/O

C/R = # of analog input channels / # of A/D voltage references

Fig. 10: ADCON1 Register.

# **END OF PAPER**